基本概念

什么是时序约束?从简单角度来说,就是从引脚或者寄存器的信号到另一个引脚或者寄存器的时间是否满足一定的时间要求。其输入信号要延迟多长时间,时钟周期是多少,通过设置,让软件在布局布线(Place and Route)时候,按照我们设置来产生电路。

建立时间/保持时间

在知道了时序约束概念后,我们还得知道两个概念,它就是建立时间和保持时间。

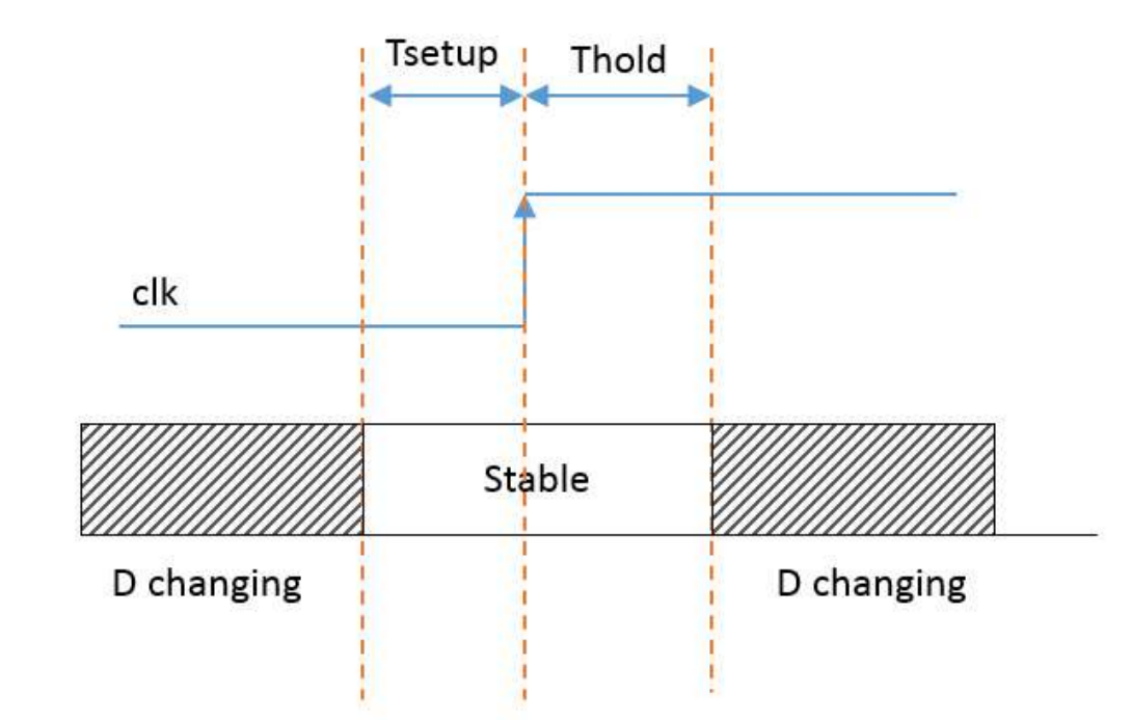

1:建立时间:对于触发器来说,在clk上升沿到来之前,数据得提前有一个“建立量”预先准备好,这个“量”就是建立时间。

2:保持时间:对于触发器来说,在clk上升沿到来之后,数据得有一个“保持量”,这个“量”就是保持时间。

时序模型

建立时间:![]()

保持时间:![]()

约束类型

1. IO约束:IO约束又为管脚约束,其主要是引脚绑定、电平标准。

2. 时钟约束:时钟约束为主时钟的频率建立,异步时钟组,虚拟时钟等。

3. 延迟约束:对于一些高速信号组,让它们在进入FPGA之前,有一个时间的延迟,让它们一起进入。

4. 多周期约束:在FPGA内部,逻辑时序较大,建立时间或者保持时间不够,我们得采用多周期约束。

5. 伪路径:通常用于跨时钟域。在跨时钟域时,肯定会有时序上的违规,在这个时候,我们将其设置为伪路径。

6. 扇出:FPGA内部的布线跨度过大,造成时序不稳定,会对其进行扇出约束。

参考内容

1. 《FPGA设计实战演练·高级技巧篇》

2. 《vivado从此开始》